Takuya Yoshioka

CAE Eng. Dept. / Product Design Key Technology R&D Div.,

DENSO CORPORATION

Abstract

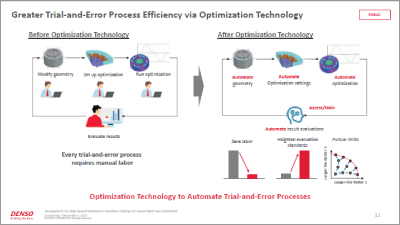

Optimization is adopted as a means of improving product‐design efficiency. It requires numerous evaluations, so that a making computational‐cost reduction is critical challenge for practical applications. JMAG provides both functionality and license called PSL that enable distributed processing of multiple designs on an HPC system from geometry modification through solver execution. In this presentation, we outline the high‐speed optimization workflow utilizing HPC‐based distributed processing and report results of a significant reduction in computation time compared with traditional sequential methods.

To read Proceedings, please sign-in.

Protected content here, for members only.You need to sign in as a Regular JMAG Software User (paid user) or JMAG WEB MEMBER (free membership).

By registering as a JMAG WEB MEMBER, you can browse technical materials and other member-only contents for free.

If you are not registered, click the “Create an Account” button.

Create an Account Sign in